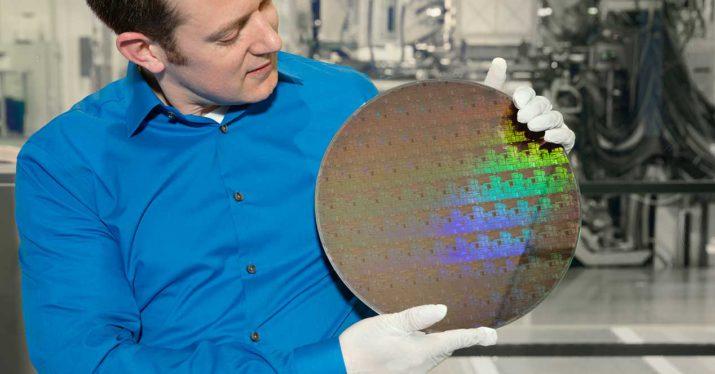

IBM da un golpe sobre la mesa y muestra el primer chip de 5 nanómetros

La Ley de Moore se ha mostrado algo complicada de mantener en los últimos tres años, debido a las complicaciones que empieza a presentar el silicio al reducirse los transistores a tamaños tan pequeños. Ahora, IBM ha presentado el primer chip de 5 nanómetros, con el que aseguran estabilidad en la industria por lo menos durante 4 años.

Los 5 nanómetros llegan de la mano de GAAFET

En la actualidad, los chips con un tamaño inferior a 22 nanómetros utilizan un método con transistores tridimensionales llamado FinFET. El problema es que este método morirá con los 7 nanómetros, que es su tope. Para llegar a los 5 nanómetros, e incluso posteriormente a los 3, se utilizará el método llamado GAAFET (Gate-all-around).

Este método supone la vuelta a un sistema bidimensional en la fabricación de chips, y se utilizará de manera conjunta con litografía ultravioleta extrema (EUV), una litografía óptica con longitudes de onda muy cortas (de 13,5 nm). De momento, nadie en la industria sabe qué llegará después de los 3 nanómetros. La llegada de chips tridimensionales solucionó el problema que presentaban las estructuras bidimensionales, en las cuales el canal era tan pequeño que lo átomos no podían transportar la electricidad lo suficientemente rápido. FinFET lo arregló añadiendo canales tridimensionales.

Ahora, IBM ha vuelto a la bidimensionalidad de la mano de Samsung y Global Foundries, utilizando para ello una estructura horizontal, frente a la vertical de FinFET. El método GAAFET usado por IBM consiste en tres nanocapas una encima de la otra encima del drenaje y la fuente, con la puerta (la parte del bit que activa y desactiva el canal) entre los huecos. Con esto, se consigue un mayor volumen de puerta y canal, haciendo que GAAFET sea más fiable, con mejor rendimiento, y con una escalabilidad aún mejor que permite llegar a los 3 nanómetros.

Hasta 2021 no los veremos en el mercado

IBM afirma que, comparado con los chips de 10 nanómetros actuales, los 5 nanómetros ofrecen una mejora de rendimiento del 40% con un mismo consumo, o una reducción del 75% del consumo de recursos al mismo rendimiento que los 10 nanómetros. La densidad de transistores también se ha disparado, pudiendo alcanzar los 30.000 millones de transistores en un chip de 5 cm2.

Mientras que los chips de 10 nanómetros acaban de llegar al mercado de la mano del Snapdragon 835 y el Exynos 8895, otras compañías de la industria como Intel todavía no han dado el paso. Incluso NVIDIA utilizará los 12 nanómetros para Volta, su nueva generación de tarjetas gráficas. Posteriormente a los 10 nanómetros llegarán los 7 nm en 2019, y ahora IBM acaba de afirmar que después de los 7 nm van a llegar los 5 nm, aunque éstos no llegarán hasta dentro de por lo menos cuatro años.

Que este tamaño tarde tanto en llegar a la industria tiene que ver con que la industria de los semiconductores prefiere optimizar procesos de fabricación y diseño de transistores antes que gastar miles de millones de dólares en desarrollar una nueva tecnología. En el futuro, empresas como Intel investigan la posibilidad de unir varios chips uno encima del otro para mejorar el rendimiento sin tener que reducir el tamaño de fabricación, a costa de disparar el consumo.

Via: www.adslzone.net

Reviewed by Zion3R

on

3:40

Rating:

Reviewed by Zion3R

on

3:40

Rating: